关于数据的读取与保存的任务已经完成,下面开始进入FPGA学习阶段。

该篇包括:FGPA的安装、FPGA的设计思路、利用一个简单的例子(二选一多路器)完成整个设计思路、固化文件的生成。

软件安装

安装软件时注意选择自己需要的硬件、库即可,不然会很大。具体操作可参考:

link

link

FPGA设计思想与验证方法

- 在电路板实现功能,在实现功能的时候积累开发和调试经验。(自己写代码,写不出来的时候看参考×;学会调试,找问题)

- 学会如何使用现成的代码?(FPGA有70%~80%是自己写)

- verilog语法,FPGA常见的设计方法。 自己写代码,下载代码进行使用,使用厂家或者第三方提供的IP核

自己写代码(状态机、线性序列机)

IP核(FIFO、RAM、ROM)

常见的接口设计,SPI、IIC、UART

例子:DDS:矩阵键盘、DAC、LCD/数码管,这些模块之间使用怎样的接口逻辑,来确保数据的正确传递。

高速数据采集系统:数据流接口的设计。

调试、分析问题的经验积累起来了,能力就培养起来了。 - 二选一多路器;三八译码器;计数器电灯;==>学习开发工具的使用

以太网接口、摄像头、VGA

一定要自己独立去写,写出问题不要怕,这是成长的机会。 - 仿真的认识:

仿真的两大作用1)检查验证设计功能是否正确;2)调试问题,仿真可以看到设计中每一个信号每一个时刻的值。通过仿真来分析设计中的信号异常原因,一步一步溯源,最终找到问题的原因并解决。

在做设计时,超过50%的时间不是在写代码,而是通过仿真调试代码找问题。

通用FPGA开发流程

verilog;状态机、线性序列机;学习仿真。

概述:写一套硬件描述语言,能够在指定硬件平台上实现相应的功能。

- 设计定义(让LED灯一秒闪烁一次);

- 设计输入(编写逻辑(使用Verilog代码描述逻辑),画逻辑图,使用IP核);

- 分析综合(有专业的EDA软件进行,Quartus、Vivado、ISE),对缩写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容;

- 功能仿真(前仿真、逻辑仿真):使用专门的仿真工具进行仿真,验证设计的逻辑功能能够实现;

仿真时理想情况,可靠度不是那么高,不要依赖仿真××

对于数字电路来说,仿真是基本接近于真实情况的,是可信的。 - 布局布线(接线会影响输出);

- 性能分析:时序仿真Modelsim(非常耗费时间)与静态时序分析;

- 下载到目标板上查看运行结果、板级调试。

ILA\Signaltap ll

最终:让设计的逻辑在目标板上正确工作,(功能正常、性能稳定)

基于Vivado的FPGA开发流程

创建工程

- 打开软件,创建工程;

- 选择器件后一直next;

- 左边点击ADD Source:选择ADD or create design sources;

- 点击create file-选择语言(verilog),文件名称与工程名一致;

开始编程

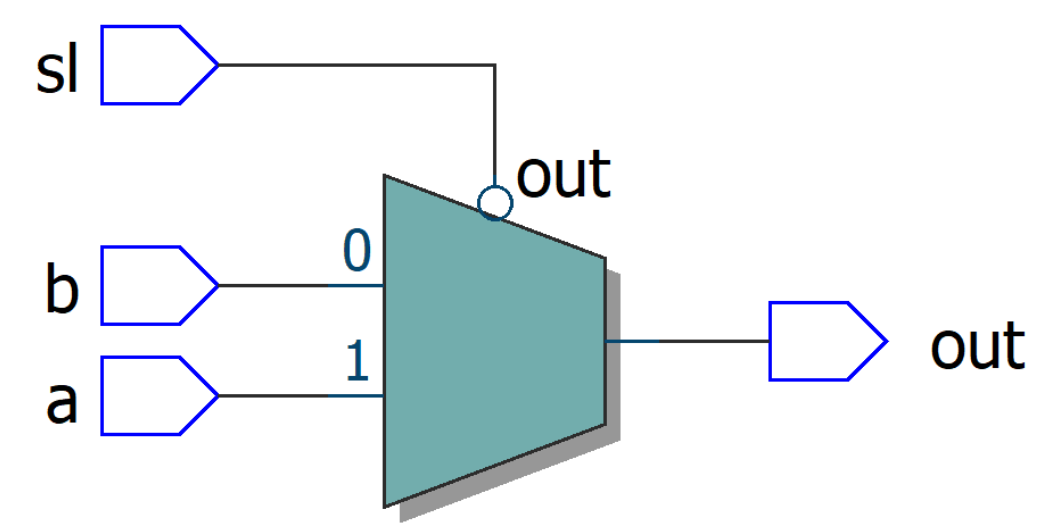

以二选一多路器为例:

SL = 1,out = a;

SL = 0,out = b;

module mux2(

a,

b,

sl,

out

); //moudle+名字+(变量定义)

input a;

input b;

input sl;

output out; //定义变量

assign out = (sl == 1) ?a : b; //赋值

endmodule //结束

分析综合

点击 run

功能仿真

ADD Sources=>Add or create simulation source=>命名Mux2_tb (tb:test bench):主要三步

`timescale 1ns / 1ns

module mux2_tb();

reg s_a;

reg s_b;

reg sl;

wire out;

mux2 mux2(

.a(s_a),

.b(s_b),

.sl(sl),

.out(out)

);//例化

initial begin

s_a = 0;s_b = 0;sl = 0;

#200;//延时200,只能在仿真处使用,在实际中无法使用#延时

s_a = 0;s_b = 0;sl = 0;

#200;

s_a = 0;s_b = 0;sl = 1;

#200;

s_a = 0;s_b = 1;sl = 0;

#200;

s_a = 1;s_b = 0;sl = 0;

#200;

s_a = 1;s_b = 1;sl = 0;

#200;

s_a = 1;s_b = 0;sl = 1;

#200;

s_a = 0;s_b = 1;sl = 1;

#200;

$stop;

end

endmodule

点击run simulation

布局布线

点击 run Implementation

实际仿真

run simulation =>run post-implementation Timing simulation

实际仿真存在时间误差

扳机调试

IMPLEMENTATION =>点击Open Implemented Design=>Layout=>I/O planing=>根据自己的板子设置端口=>ctrl+S保存=>Gennerate Bitstream=>open hardware manager=>open target

创建工程写代码,进行仿真,分析仿真结果与设计是否一致。

MCS文件的生成及烧录

MCS文件的生成及烧录

link